�ؼ��ʣ�cpu����

ʱ�䣺2025-08-27 14:04:24 ��Դ���е���

�����Ǿ�о�ܣ��칹��������ӮAIʱ���������Ŀ�Ļ�ݽ�

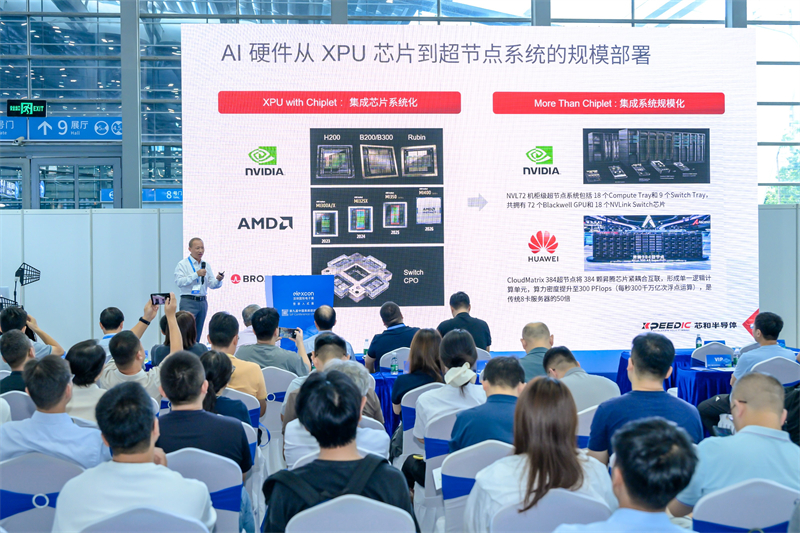

��2025��8��26�գ��й�����Ѷ——���գ��ھŽ��й�ϵͳ����װ��ᣨSiP Conference China 2025�������ڻ�չ���ģ����¡�ؿ�Ļ��о�Ͱ뵼�崴ʼ�ˡ��ܲô�������ʿ�ٴ��Դ����ϯ���ݷ�����Ϊ���Ǿ�о�ܣ��칹��������ӮAIʱ���������Ŀ�Ļ�ݽ����Ӳ�ҵ�߶�ϵͳ��������AI�������������£�Chiplet�Ƚ���װ���������ٵĻ�������ս����������ҵ��Я�ֹ�������Эͬ��Chiplet��̬ϵͳ��

����ʿָ�����й�ϵͳ����װ�������ǵھŽ졣����һ���֤��ϵͳ����װ���Ƚ���װ�ĸ��ٷ�չ�ľ��꣬��ӭ����һ���µ������㣺���Ź���Ժ����������ʵʩ“�˹�����+”�ж������������أ�AI�˹������Ѿ�������Ϊ���Ĵ�“��ҵ����”�ĺ�����������Ӧ�ó��������ϵش��ƶ�ѵ�����������ն�Ӧ�������뵼������������������������������ܶ�����˾���������ս��Ȼ��������Ħ�����ɱƽ��������ޣ���������SoC��оƬ���������������������Ѵ���Ż���ϵͳ�����Ѿ���Ϊ����������һ���棬оƬϵͳ��——��άоƬChiplet�Ƚ���װ���칹�������ڳ�Ϊ�������������ĺ���·��������Ӣΰ�AMD����ͨ��AIоƬ��ͷ�㷺���ã���һ���棬ϵͳ��ģ��——��Ӣΰ��NVL72����Ϊ�N��384�����ڵ�ϵͳΪ����������ϵͳ����ͨ��������ڵĸ����ٻ�����������ͻ��scale up��scale out�����ܱ߽硣AI ���ڵ�Ӳ��ϵͳ������Chiplet���ɼ������ں�����Ϊ��Ħ��ʱ���Ƚ������Ƴ�ƿ������������ͻ�Ƶ���Ҫ����

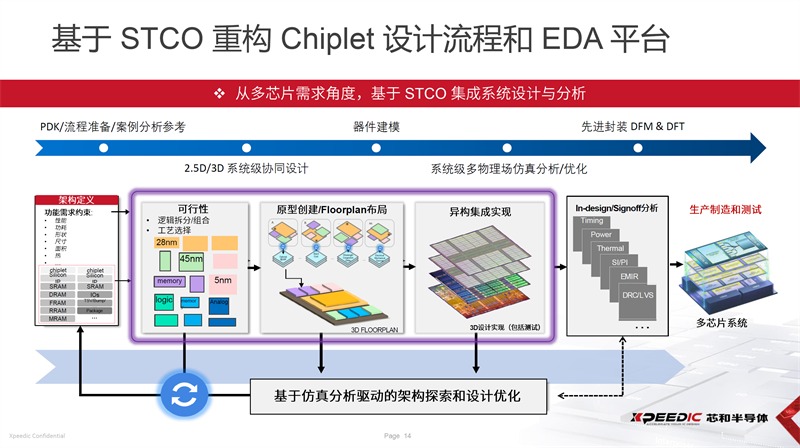

��������ζ�����µ�������Ҫ�������Chiplet ����ϵͳ���ٸ��ܻ��������ٴ��š���-��-����ϼ������Ż������������ս�������AI���ڵ�Ӳ��ϵͳ�����������Ż�����ѹֱ����Դ������ơ�Һ��ϵͳ��оƬ����Ϸ��棬�临�Ӷ�ҲԶ����ͳ��оƬ��Ƶ������߽硣��Щ����Ҫ����Ʒ�ʽ�Ӵ�ͳ�ĵ����Ż���DTCO����ƹ���Эͬ�Ż���������ȫ��·Эͬ��STCO��ϵͳ����Эͬ�Ż�����Ϊ����Chiplet��ҵ�������˹����ķ�չ������

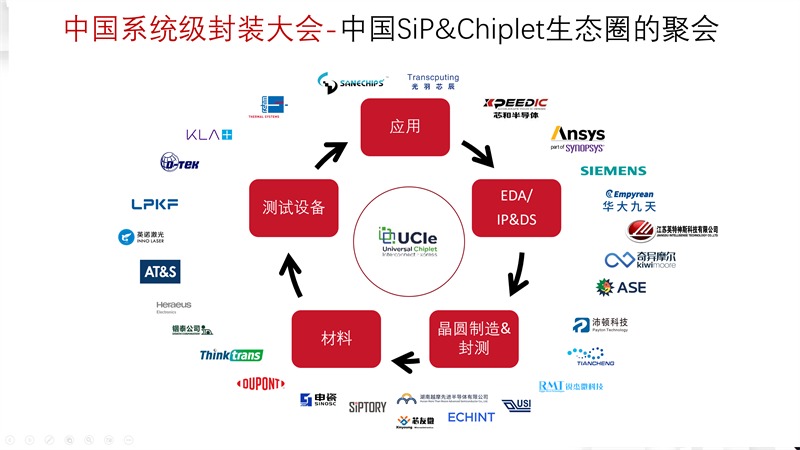

�����õ��ǣ�����UCIe3.0�ķ������Լ�����OCP��OIF��3DLink��CCITA�ȹ�����Chiplet��������غͳ��죬Chiplet ��̬����“Ӣΰ��ʽ”��ȫ���ģʽ�������Կ��ű�ΪŦ����“ƴ���ģʽ”���й����ն˳����������������г�������߱��������ƣ����ƶ���Ԫ���̡���սڵ㡢��IP��Դ���칹���ɳ�Ϊ����������ʿ��������Chiplet�Ƚ���װ��ҵ��ÿ�����ڵ���ҵ����������֡�ǿ�����ϣ����ա���ơ����̺�EDA���ߵȿ绷��Э��������“оƬ-��װ-ϵͳ-Ӧ��”��ȫջ����������AI������ʱ�������������ܹ���AI��ҵ��ȫ������������ռ��������

���δ�������˼�ʮ���й�ϵͳ����װ��Chiplet�Ƚ���װ��̬Ȧ��ͷ����ҵ��ͬ����̽�֡��ڴ�����յ���ּ�ݽ����ڣ�����о�Ͱ뵼�壬������������������о�������¹⡢������ӡ��麣��ɵ���ҵ�ĸ߹ܺ�ר�����Chiplet�Ƚ���װ�IJ�ͬ�������˶��ұ��档

����о�Ͱ뵼��

о�Ͱ뵼��Ƽ����Ϻ����ɷ�����˾�����¼��“о�Ͱ뵼��”����һ�Ҵ��µ�������Զ�����EDA�����������з��ĸ��¼�����ҵ��Χ��“STCO����ϵͳ���”����ս�Բ��֣�����SI/PI/���/����/Ӧ���ȶ��������漼������“�����������”������ṩ��оƬ����װ��ģ�顢PCB�弶������������ϵͳ��ȫջ����ϵͳEDA���������֧��Chiplet�Ƚ���װ�������ڸ��ܺͼ�����һ�����ٸ�Ƶ���ܵ��Ӳ�Ʒ����ƣ�����5G�������ֻ������������˹����ܺ��������ĵ�����õ��㷺Ӧ�á�

о�Ͱ뵼�����ٻ���ҿƼ�������һ�Ƚ������Ҽ�ר������С������ҵ����������˾��Ӫ���з��ܲ�λ���Ϻ��Ž��������ݡ��人�����������������з������ģ��ڱ��������ڡ��ɶ��������ȵ��������ۺͼ���֧�ֲ��š������˽�������飬�������www.xpeedic.com��

��������

����ϲ��